Getting Started with OVM. Introduction Constrained randomization is a great way to find bugs quickly and thoroughly explore a design's state space, quickly reaching 100% design coverage.

OVM's built-in randomization, hierarchial stimulus (sequences), and testbench architecture are designed from the ground-up to accomodate a constrained-random stimulus verification environment. When coming from a directed testing background, it is very tempting to incorporate self-checks directly into the hierarical sequences—and indeed, there may be cases where this is necessary. However, the best approach is to use monitors on each interface, which send observed transactions to a scoreboard where the behavior is then checked for correctness.

This frees up the stimulus to be more flexible, reusable, and of course, random. Instead, a better approach is to create an accurate shadow model of the design's registers, which the scoreboard can use to model and determine the correct behavior of the design. Register Packages <? Wow! Welcome - Magillem. Magillem provides to customers in the electronic industry tools and services that drastically reduce the global cost of complex design.

Magillem has developed an easy to use, state of the art platform solution to cover electronic systems design flow challenges in a context where complexity, interoperability and design re-use are becoming critical issues to manage design cycle time of SOC. Register Verification. IDesignSpec™ (IDS) : Executable Design Specification Tool & UVM Registers See short demo video | Download Brochure | Frequently Asked Questions IDesignSpec™ is an award winning engineering tool that allows an IP, chip or system designer to create the register map specification once and automatically generate all possible views from it.

Various outputs are possible such as UVM, OVM, RALF, SystemRDL, IP-XACT etc. User defined outputs can be created using Tcl or XSLT scripts. IDesignSpec’s PATENTED technology improves engineer’s productivity and design quality. EDA-STDS.ORG Home Page. IP-XACT. IP-XACT is an XML format that defines and describes electronic components and their designs.

IP-XACT was created by the SPIRIT Consortium as a standard to enable automated configuration and integration through tools.[1] The goals of the standard are to ensure delivery of compatible component descriptions from multiple component vendors,to enable exchanging complex component libraries between electronic design automation (EDA) tools for SoC design (design environments),to describe configurable components using metadata, andto enable the provision of EDA vendor-neutral scripts for component creation and configuration (generators, configurators).

Approved as IEEE 1685-2009 on December 9, 2009, published on February 18, 2010.[2] Tools[edit] References[edit] 1685-2009 – IEEE Standard for IP-XACT, Standard Structure for Packaging, Integrating, and Reusing IP within Tools Flows. 2010. doi:10.1109/IEEESTD.2010.5417309. Further reading[edit] External links[edit]

Verification Horizons - February 2010. Home - Accellera Systems Initiative. Standard Association - IEEE Get Program. IP-XACT - Accellera Systems Initiative. Charter.

XML Schema - Accellera Systems Initiative. Posted for reference by Accellera Systems Initiative.

/XMLSchema. 1685-2009 - Accellera Systems Initiative. Posted for reference by Accellera Systems Initiative.

/XMLSchema/SPIRIT/1685-2009 © Copyright 2006-2013 Accellera Systems Initiative. All rights reserved. These XML files are believed to be a consistent XML Schema expression for creating and validating XML documents based on the IEEE Std 1685-2009 Standard for IP-XACT, Standard Structure for Packaging, Integrating and Re-using IP within Tool-flows. These files are in the format specified by the World Wide Web Consortium (W3C) as XML Schema definition language.

PDTi. Free Science & Engineering software downloads. IDesignSpec : Register Generator. Verification Management Tool – Agnisys.Com. Ids.png (1239×1726) Funbase IP library. Details Name: funbase_ip_library Created: Sep 27, 2011 Updated: May 8, 2012 SVN Updated: Jun 17, 2013 SVN: Browse Latest version: download Statistics: View Other project properties Category: Library Language: VHDL Development status: Planning Additional info: none WishBone Compliant: No License: LGPL Description Funbase project focuses on FPGA-based embedded product development.

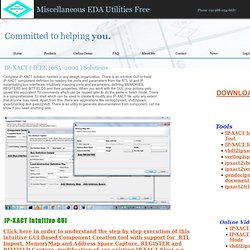

OpenCores. Complete IP-XACT Solution. Committed to helping you.

Miscellaneous EDA Utilities Free IP-XACT ( IEEE 1685 -2009 ) Solutions Complete IP-XACT solution needed in any design organization. There is an intuitive GUI to build IP-XACT component defintion by reading the ports and parameters from the RTL of and IP, instantiating bus interfaces, intuitively mapping ports and parameters, defining MEMORIES, REGITERS and BITFIELDS and their properties. When you work with the GUI, your actions gets saved into equivalent Tcl commands which can be reused later to do the same in batch mode. If you have any question concerning bug fixes, new features and enhancements, please don't hesitate to contact.

Extract the compressed package and cd to the installation directory, read the README file in that directory. Source the script setup_env( .csh or .sh or .bat as applicable ) look into the example directory to get a sense of this tools. It is assumes that you have Java 1.6 installed in your machine and its accessible. source setup_env. or.

Miscellaneous EDA Utilities.